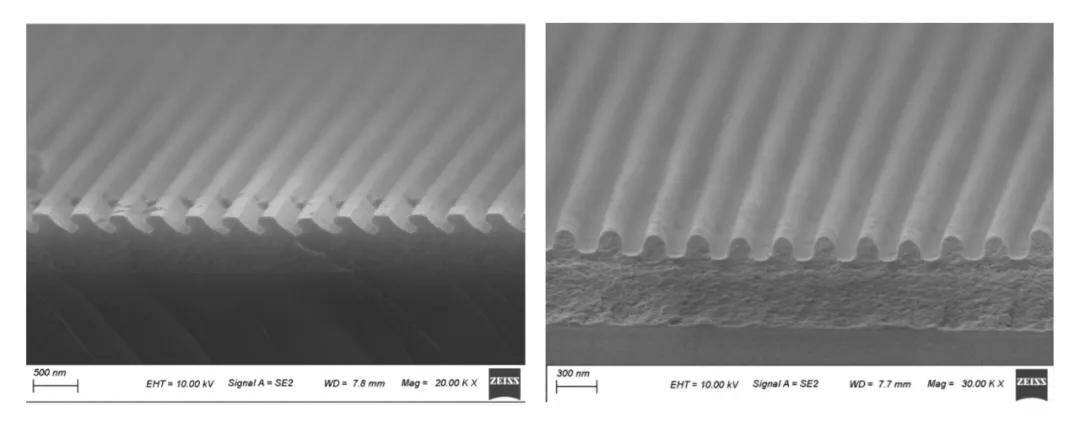

IC tasarım, yani entegre devre tasarımı, nano süreç teknolojisi içinde yüksek hassasiyet gösterir ve hassasiyet ne kadar yükseksede, üretim süreci o kadar ileri seviyededir. İşlemciye daha fazla transistör entegre edildikçe, çip daha fazla işlev kazanır ki bu da doğrudan işlemcinin üretim maliyetini düşürür. Ancak, entegre devrelere ait süreç düğümleri küçüldükçe, kritik boyut ölçümünde de büyük zorluklar ortaya çıkar. Nano yapı dönemleri, çizgi genişliği, çizgi yüksekliği, yan duvar açısı ve kabartma gibi geometrik morfoloji bilgilerini ölçmek ve analiz etmek son derece önem taşır.

Çözüm:

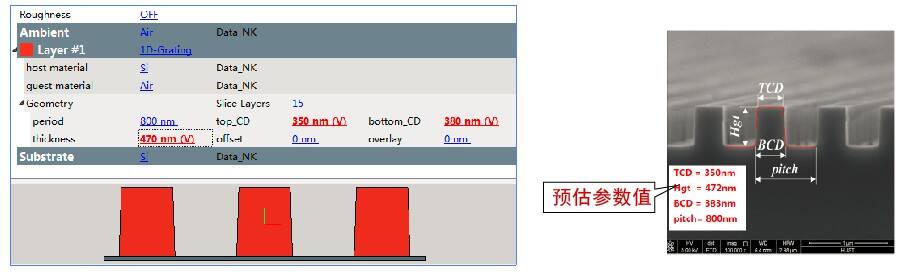

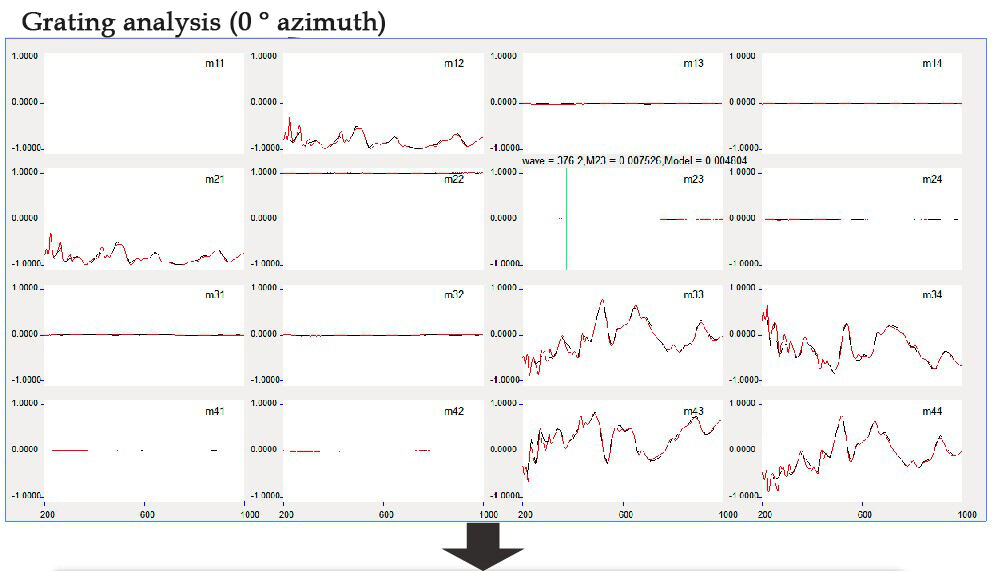

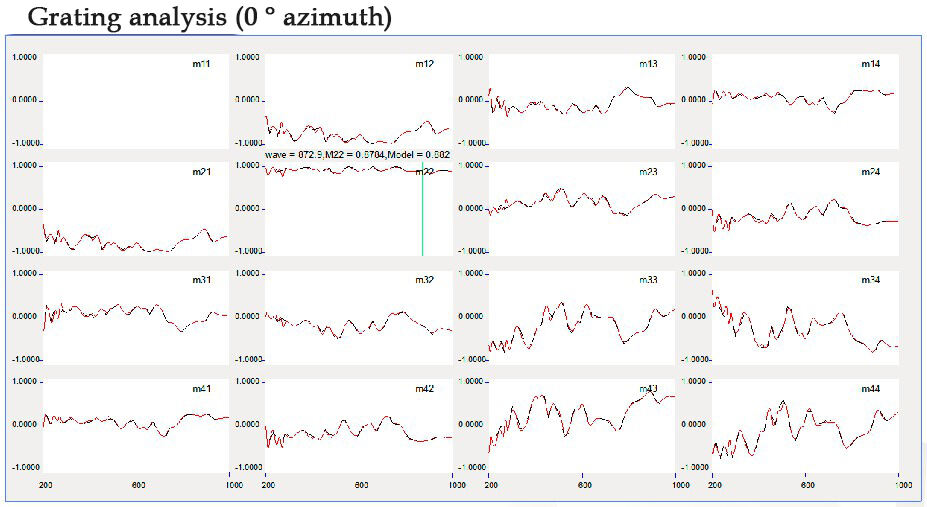

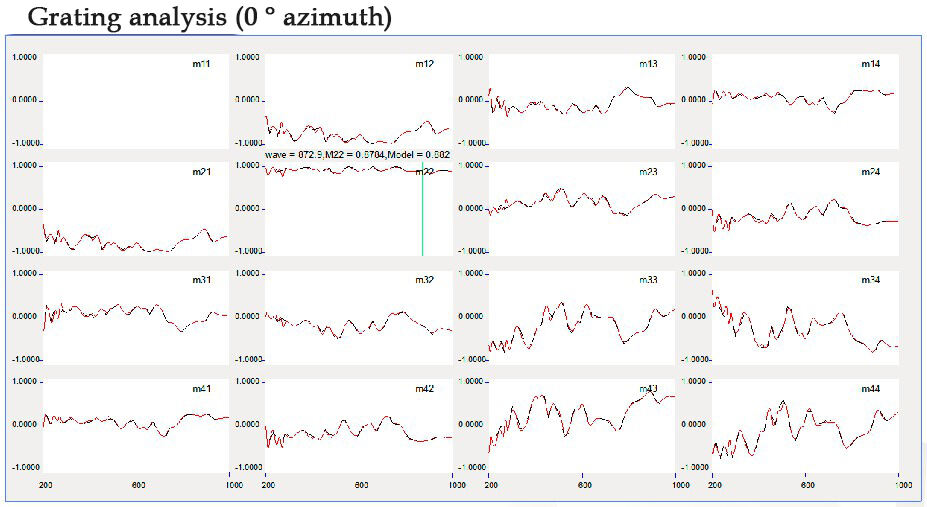

Mueller matrisi elyozometri ölçümü kullanılarak 16 küme kutuplaşma bilgisi elde edildi ve daha doğru elyozometri parametreleri (PSI: amplitud oranı, △: faz farkı) bulundu. Yüzlerce iç yapılandırılmış optik model uyum için kullanıldı ve ardından nano yapı dönemleri, çizgi genişliği, çizgi yüksekliği, yan duvar açısı ve kabartma gibi geometrik morfoloji bilgileri ölçüldü ve analiz edildi.

Optik model oluştur

Kutuplama elemanı bilgisi

Telif Hakkı © Guangzhou Minder-Hightech Co.,Ltd. Tüm Hakları Saklıdır