Dizainas IC, kuris taip pat vadinamas integruotojo dizainu, turi aukšto tikslumo nano technologijose, ir kuo aukštesnis tikslumas, tuo sudėtingesnis gamybos procesas. Kai į procesorą integruojama daugiau tranzistorių, čipas gali atlikti daugiau funkcijų, kas tiesiogiai sumažina procesoriaus gamybos išlaidas. Tačiau kai integruotųjų grandynų procesiniai mazgai tampa mažesni, kritinio dydžio matavimui taip pat kilsta dideli iššūkiai. Ypač svarbu matuoti ir analizuoti geometrinius formos duomenis, tokiais kaip nanostruktūros periodas, linijos plotis, linijos aukštis, šoninio dangu kampas ir rūgštis.

Sprendimas:

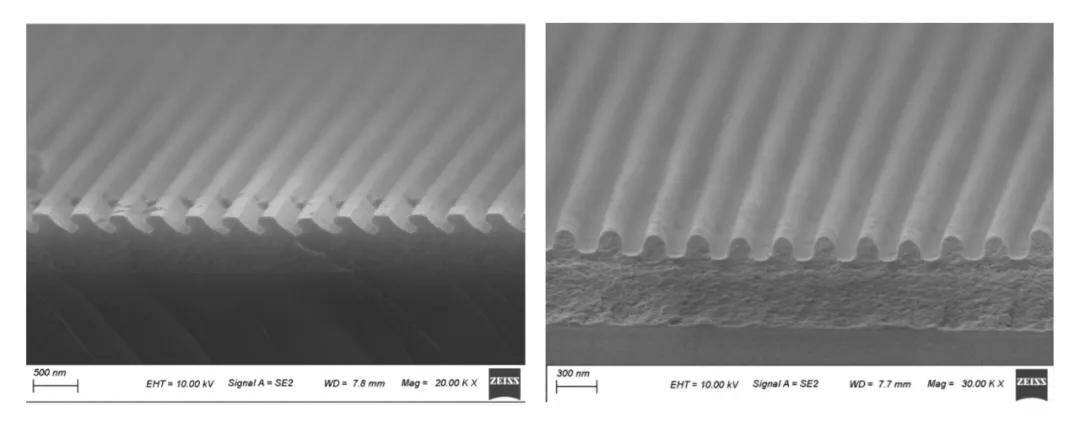

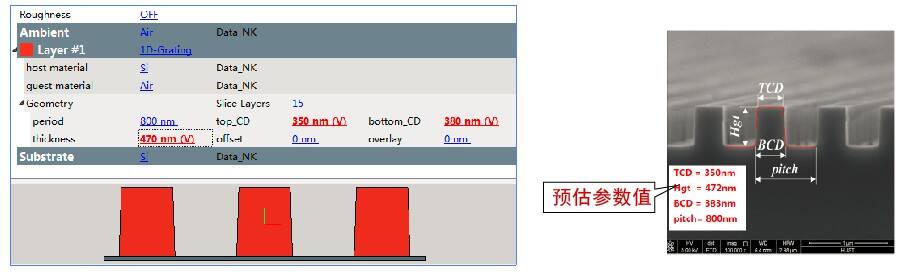

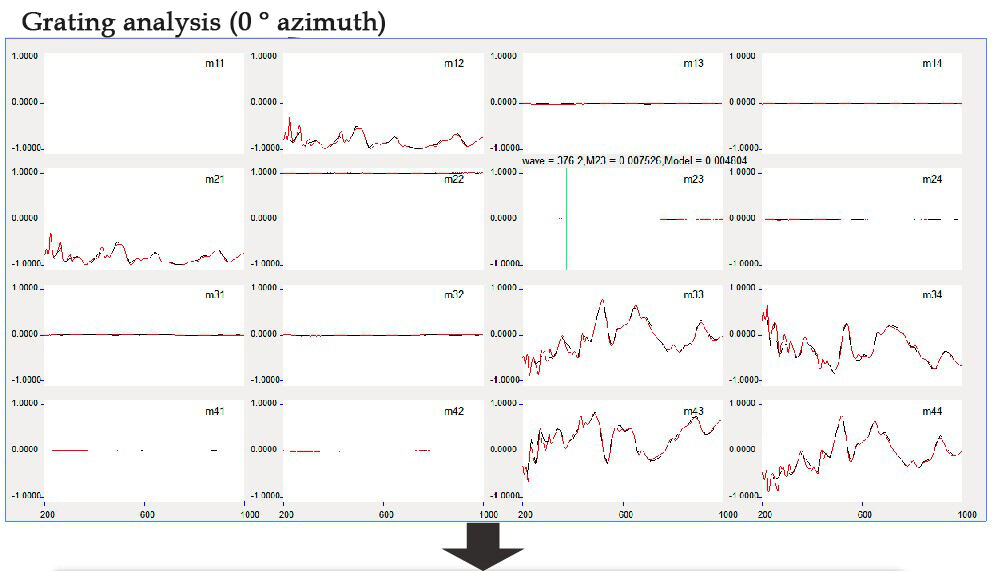

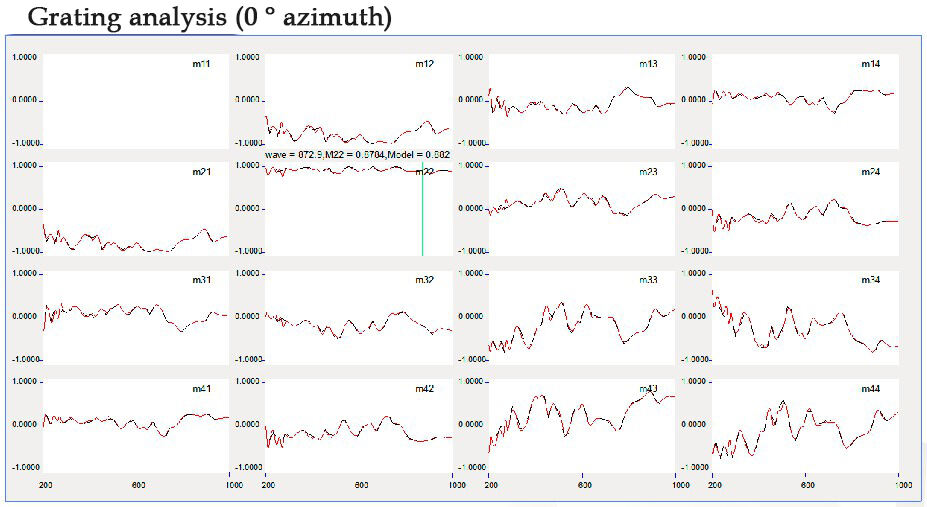

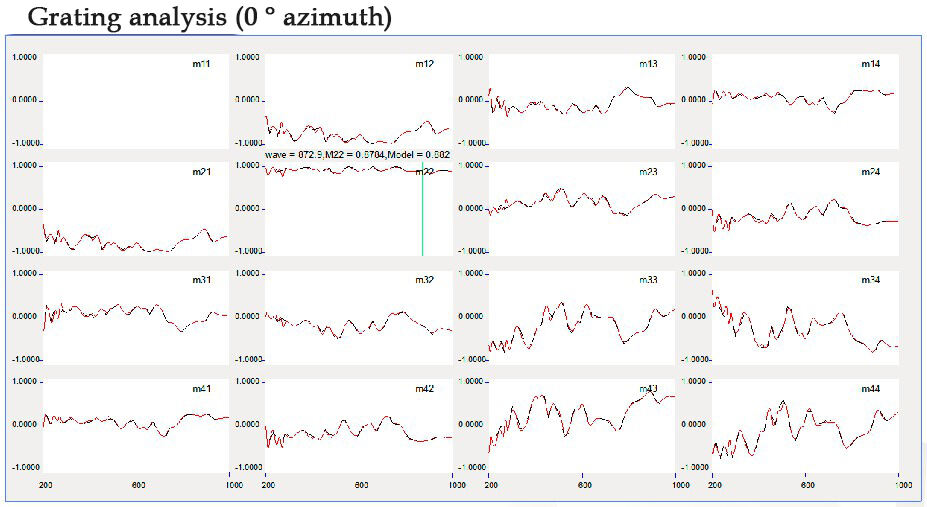

Naudojant Mueller matricos elipsometrijos matavimą, buvo gauti 16 poliarizacijos informacijos rinkiniai ir gresniau nustatyti elipsometrijos parametrai (PSI: amplitudinių santykių, △: fazės skirtumas). Jukybentoptinių modelių buvo naudojama derinimo metodu, o vėliau buvo matuojama ir analizuojama geometrinė informacija apie nanostrukčių periodą, linijų plotį, aukštį, šoninio sienelės kampą ir rūgštį.

Sukurti optinį modelį

Poliarizacijos elementų informacija

Copyright © Guangzhou Minder-Hightech Co.,Ltd. Visos teisės saugomos